# MOSFET Channel Engineering and Scaling Study using COMSOL®

D.Subedi<sup>1</sup> and D. A. Fixel<sup>1</sup> 1. Dept. of Engineering , Trinity College, 300 Summit Street, Hartford, CT 06106, USA

## Introduction

With the scaling of semiconductor devices into the nanometer regime, short channel effects such threshold voltage instability, reduced output as punch-through and resistance, hot-electron degradation persist. As the traditional formulae fail to compute current, threshold voltage, and electric fields for FIBMOS, COMSOL Multiphysics is used to study the effect of constant-field scaling on a FIBMOS device compared to the conventional MOSFET.

Figure 1. Two different user-controlled meshes designed for the simulation

#### **COMSOL Multiphysics Model**

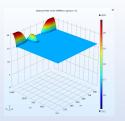

COMSOL Multiphysics<sup>®</sup> with the Semiconductor Module (semi) is used to design the 2D models of the silicon devices. A narrow P+ region is implanted next to the source region to make a FIBMOS device. Two different user-controlled meshes are generated according to the need of the simulations. Mobility and Recombination models that encapsulate the physics are incorporated and solver settings are modified accordingly. Building on the work done in [1], we conduct simulations on conventional MOSFETs as well as FIBMOS transistors for 122.5-nm, 175-nm, 245-nm, and 350-nm channel-length devices using a parametric sweep on k (scaling parameter) for values of 0.35, 0.5, 0.7, and 1.

$$\begin{aligned} \nabla \cdot (-\epsilon_0 \epsilon_r \, \nabla V) &= q(p-n+N_d^+ - N_a^-) \\ J_n &= qn\mu_n \nabla E_c + \mu_n k_B T G\left(\frac{n}{N_c}\right) \nabla n + qn D_{n,\text{th}} \nabla \ln(T) \\ J_p &= qp\mu_p \nabla E_v + \mu_p k_B T G\left(\frac{p}{N_v}\right) \nabla p - qp D_{p,\text{th}} \nabla \ln(T) \\ &\qquad \frac{\partial n}{\partial t} = \frac{1}{q} \left(\nabla \cdot J_n\right) - U_n \\ &\qquad \frac{\partial p}{\partial t} = -\frac{1}{q} \left(\nabla \cdot J_p\right) - U_p \end{aligned}$$

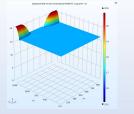

Figure 2. Doping Profile of the Conventional MOSFET.

Figure 3. Doping Profile of the

**FIBMOS** transistor.

## Results

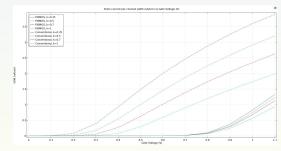

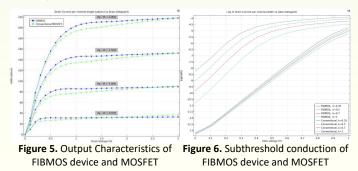

Figure 4. shows the transfer characteristics of the conventional MOSFET and FIBMOS device with varying channel lengths for very low voltage which demonstrates threshold voltage stability of the FIBMOS device. Figure 5. shows the output characteristics of the devices with 350-nm channel length. The nearly zero slope in the saturation region for FIBMOS device shows significantly improved output resistance. Figure 6. shows a plot of Id vs Vg in the subthreshold range of the devices. The drain current for FIBMOS device is very low and consistent for varying channel length indicating that FIBMOS device has greater resistance against punchthrough effect compared to the conventional MOSFET.

Figure 4. Transfer Characteristics of FIBMOS device and MOSFET

#### Conclusion

Extracting results for transistor devices of this scale is difficult. COMSOL **Multiphysics**<sup>®</sup> extremely Semiconductor Module is useful for predicting currents and electric fields of MOSFET devices. The FIBMOS device shows better output resistance, threshold stability, and greater resistance against punch-through. Hence it demonstrates properties closer to the ideal transistor compared to the Conventional MOSFET.

#### References

- 1. Chih-Chieh Shen et al., Use of Focused-Ion-Beam and Modeling to Optimize Submicron MOSFET Characteristics. IEEE Transactions on Electron Devices 45, no. 2, Page no: 453-459, (February 1998)

- 2. Neamen, Donald A. Semiconductor Physics and Devices: Basic Principles. 4th ed, McGraw-Hill, (2012).